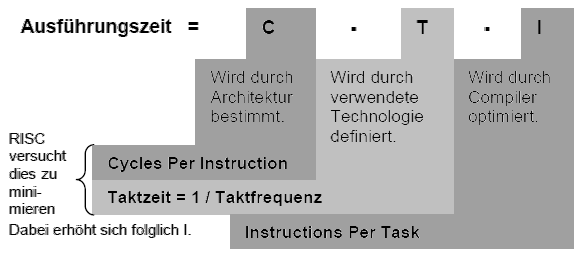

Die Prozessorleistung ist umgekehrt proportional zur Ausführungszeit eines

Algorithmus und wird aus folgenden drei Parametern ermittelt:

RISC Architekturen sind darauf aus, die Cycles Per Instruction zu minimieren. Das heißt, es wird versucht alle Befehle mit so wenig wie möglich Takten auszuführen.

Welche architektonischen Möglichkeiten gibt es zur Veringerung der CPI?

Piplining ergibt eine CPI > 1, andere Techniken wie Superskalarität und

VLIW's haben Ausführungszeiten von kleiner als eins. Kombiniert ergeben beide

Ansätze eine nahezuhe Ausführung von einem Befehl pro Takt.

Desweiteren ermöglicht der kleine Befehlssatz von RISC eine festverdrahtete Steuereinheit, anstatt von Mikroprogrammen, welche höhere Taktzahlen pro Befehl mit sich bringen. Desweiteren muss bei einem Risc-Befehl nicht der Op-Code dekodiert werden, um herauszufinden, wie der Befehl zu entschlüsseln ist, da alle Befehle die gleiche Struktur besitzen.

Auf welche vier Merkmale wird beim RISC-Design-Entwurf besonders geachtet?- einfache Maschinenbefehle und Adressierungsarten mit einheitlichen Befehlsformat

- große und universelle Registersätze, für schnelle Variablenverarbeitung und größere Optimiermöglichkeiten für Compiler

- Verzahnung von Compiler und Architektur zur Bereitstellung von optimierenden Compilern

- Optimierte VLSI-Chipfläche durch platzsparende Steuerwerke schafft mehr Platz für Optimiertechniken wie Pipelining,Branch-Prediction oder Superskalarität

- Parallelität von einzelnen Befehlsphasen durch Pipelining

- Parallelität von ganzen Befehlen durch Superskalartechnik und VLIW

- Parallelität von Kodefäden durch Multithreading (programmierte Parallelität) oder Multiskalarität (Hardwarethreaderkennung)

- Parallelität von Befehlen unabhängiger Algorithmen (Multiprozessorsysteme)

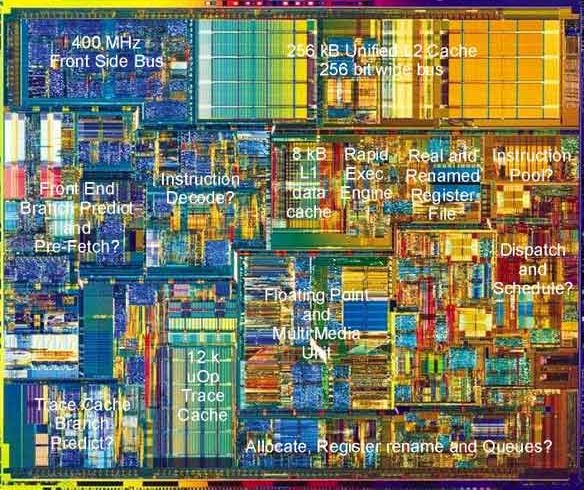

Pentium 4 Prozessor Kern

Load / Store Architektur und Lokalhalten von Daten

Da Speicherzugriffe in Pipelines starke Konflikte hervorrufen, gibt es bei RISC-Befehlssätzen nur eine einzige Möglichkeit mit LOAD bzw. STORE auf den Speicher zuzugreifen. So werden Registerzugriffe von Speicherzugriffen getrennt. Da Speicherzugriffe bekanntermaßen immer sehr viel Zeit kosten, versucht man diese so weit wie möglich zu vermeiden. Dies Erreicht man durch Lokalhalten von Daten, bzw. das Arbeiten auf den Registern.

Was sind Registerfenster?Registerfenster sollen das Lokalhalten von Daten unterstützen. Typische RISC Prozessoren wie die Berkeley RISC besitzen weit über 100 Register, von denen aber immer nur 32 für sichtbar sind:

- R0...R9 globale Register

- R10...R15 Ausgaberegister

- R16...R25 lokale Register

- R26...R31 Eingaberegister

Die Idee ist nun, daß die ersten 10 Register von allen Prozeduren gesehen werden. Die Restlichen von R10 bis R31 sind jeweils nur einer Prozedur zugeordnet. Falls nun eine Prozedur eine andere aufruft, wird nur das "Fenster" auf einen freien Registerbereich umgeschaltet. So müssen die Register nicht neu aus dem Speicher geladen werden und es wird dadurch viel Zeit gespart. Normalerweise überlappen sich die einzelnen Fenster um einige Register, um somit gleich eine effiziente Möglichkeit der Parameterweitergabe zu bieten.

Was passiert wenn alle Registerfenster voll sind?

Bei unserem Beispiel mit 138 Registern sind nach sieben Prozeduraufrufen alle Register gefüllt. Um ein Überlaufen zu vermeiden, wird das Register als Ringregister organisiert. Sind alle Registerfenster voll, wird das Älteste in den Speicher ausgelagert, was von sogenannten Trap-Routinen erledigt wird.

Was sind Superpipelines?

Superpipes vereinen Arithmetisches und Befehlspipelining. Arithmetisches

Pipelining ist sogenanntes Funktionspipelining, bei dem einzelne Phasen eines

Befehles in einer Pipeline-Form organisiert werden.

Bei Instruction Pipelining wird die Abarbeitung eines gesamten Befehls in einer

Pipeline organisiert.

Zusammenfassung Risc

- Einfachere Befehlssätze mit ca. 40-80 Befehlstypen

- Einfachere Steuerung durch die Hardware ohne Mikroprogramme

- Effizientere Pipelines durch gleichlange, eintaktige Stufen

- Befehle können meist in einem Takt ausgeführt werden

- Datenzugriffe nur durch Load und Store um Speicherzugriffe zu vermeiden

- Mehr Register und Optimierung des Befehlssatzes durch Compiler

Typische Riscsysteme haben eine hartverdrahtete Steuereinheit und somit keinen Mikrocodespeicher. Der Pentium ist ein "hybrid"-System mit RISC Kern. Dabei werden komplexe CISC Befehle durch ein Mikroprogramm in RISC zerlegt und im Kern ausgeführt. Die einfachen Befehle werden direkt im RISC Kern in einem einzigen Datenzyklus ausgeführt. Alle wichtigen elementaren (Risc) Befehle werden direkt von Level 0 ( der Hardware ) ausgeführt und somit nicht via Mikroinstruktionen interpretiert. Dies ist ein Vorteil von reinen RISC Systemen, welche diese Interpretationsebene zwischen Hardware und ISA (Instruction Set Architecture) Ebene nicht durchlaufen müssen. Mikroinstruktionen steuern den Datenweg für einen Zyklus. Sie enthält alle notwendigen Bit-Belegungen für ALU, MEM, Register etc., um einen Zyklus abarbeiten lassen zu können. Die Adresse der nächsten Mikroinstruktion wird ebenso mit codiert, wie die Art und Weise des Aufrufes. Die Mikroinstruktionen werden in einem Steuerspeicher gehalten, welcher das jeweilige Mikroprogramm enthält. Der Steuerspeicher muss die Mikroinstruktionen nicht in geordneter oder sequentieller Folge enthalten, wie es beim Hauptspeicher der Fall ist. Es kann jede Instruktion einen Verweis auf die Nächste enthalten. Sprünge sind einfach möglich. Angewandt wird dies in Form von Opcodes, welche nichts anderes als Adressen auf Mikroinstruktionen im Steuerspeicher sind.

Grundprinzipien der Rechnerarchitektur

er liegen, werden in kontinuierlicher Folge abgespeichert. Gepaart mit multiple branch prediction können mehrere zusammenhängende Basisblöcke parallel gefetched werden. (ergibt hohe issue rate) <span>Kapitel 5 - Risc Wie berechnet sich die Prozessorleistung? Die Prozessorleistung ist umgekehrt proportional zur Ausführungszeit eines Algorithmus und wird aus folgenden drei Parametern ermittelt: Worum geht es im Besonderen bei einer Risc-Architektur? RISC Architekturen sind darauf aus, die Cycles Per Instruction zu minimieren. Das heißt, es wird versucht alle Befehle mit so wenig wie möglich Takten auszuführen. Welche architektonischen Möglichkeiten gibt es zur Veringerung der CPI? Piplining ergibt eine CPI > 1, andere Techniken wie Superskalarität und VLIW's haben Ausführungszeiten von kleiner als eins. Kombiniert ergeben beide Ansätze eine nahezuhe Ausführung von einem Befehl pro Takt. Desweiteren ermöglicht der kleine Befehlssatz von RISC eine festverdrahtete Steuereinheit, anstatt von Mikroprogrammen, welche höhere Taktzahlen pro Befehl mit sich bringen. Desweiteren muss bei einem Risc-Befehl nicht der Op-Code dekodiert werden, um herauszufinden, wie der Befehl zu entschlüsseln ist, da alle Befehle die gleiche Struktur besitzen. Auf welche vier Merkmale wird beim RISC-Design-Entwurf besonders geachtet? einfache Maschinenbefehle und Adressierungsarten mit einheitlichen Befehlsformat große und universelle Registersätze, für schnelle Variablenverarbeitung und größere Optimiermöglichkeiten für Compiler Verzahnung von Compiler und Architektur zur Bereitstellung von optimierenden Compilern Optimierte VLSI-Chipfläche durch platzsparende Steuerwerke schafft mehr Platz für Optimiertechniken wie Pipelining,Branch-Prediction oder Superskalarität Techniken zur Ablaufparallelisierung für RISC-Kerne Parallelität von einzelnen Befehlsphasen durch Pipelining Parallelität von ganzen Befehlen durch Superskalartechnik und VLIW Parallelität von Kodefäden durch Multithreading (programmierte Parallelität) oder Multiskalarität (Hardwarethreaderkennung) Parallelität von Befehlen unabhängiger Algorithmen (Multiprozessorsysteme) Pentium 4 Prozessor Kern Load / Store Architektur und Lokalhalten von Daten Da Speicherzugriffe in Pipelines starke Konflikte hervorrufen, gibt es bei RISC-Befehlssätzen nur eine einzige Möglichkeit mit LOAD bzw. STORE auf den Speicher zuzugreifen. So werden Registerzugriffe von Speicherzugriffen getrennt. Da Speicherzugriffe bekanntermaßen immer sehr viel Zeit kosten, versucht man diese so weit wie möglich zu vermeiden. Dies Erreicht man durch Lokalhalten von Daten, bzw. das Arbeiten auf den Registern. Was sind Registerfenster? Registerfenster sollen das Lokalhalten von Daten unterstützen. Typische RISC Prozessoren wie die Berkeley RISC besitzen weit über 100 Register, von denen aber immer nur 32 für sichtbar sind: R0...R9 globale Register R10...R15 Ausgaberegister R16...R25 lokale Register R26...R31 Eingaberegister Die Idee ist nun, daß die ersten 10 Register von allen Prozeduren gesehen werden. Die Restlichen von R10 bis R31 sind jeweils nur einer Prozedur zugeordnet. Falls nun eine Prozedur eine andere aufruft, wird nur das "Fenster" auf einen freien Registerbereich umgeschaltet. So müssen die Register nicht neu aus dem Speicher geladen werden und es wird dadurch viel Zeit gespart. Normalerweise überlappen sich die einzelnen Fenster um einige Register, um somit gleich eine effiziente Möglichkeit der Parameterweitergabe zu bieten. Was passiert wenn alle Registerfenster voll sind? Bei unserem Beispiel mit 138 Registern sind nach sieben Prozeduraufrufen alle Register gefüllt. Um ein Überlaufen zu vermeiden, wird das Register als Ringregister organisiert. Sind alle Registerfenster voll, wird das Älteste in den Speicher ausgelagert, was von sogenannten Trap-Routinen erledigt wird. Was sind Superpipelines? Superpipes vereinen Arithmetisches und Befehlspipelining. Arithmetisches Pipelining ist sogenanntes Funktionspipelining, bei dem einzelne Phasen eines Befehles in einer Pipeline-Form organisiert werden. Bei Instruction Pipelining wird die Abarbeitung eines gesamten Befehls in einer Pipeline organisiert. Zusammenfassung Risc Einfachere Befehlssätze mit ca. 40-80 Befehlstypen Einfachere Steuerung durch die Hardware ohne Mikroprogramme Effizientere Pipelines durch gleichlange, eintaktige Stufen Befehle können meist in einem Takt ausgeführt werden Datenzugriffe nur durch Load und Store um Speicherzugriffe zu vermeiden Mehr Register und Optimierung des Befehlssatzes durch Compiler Typische Riscsysteme haben eine hartverdrahtete Steuereinheit und somit keinen Mikrocodespeicher. Der Pentium ist ein "hybrid"-System mit RISC Kern. Dabei werden komplexe CISC Befehle durch ein Mikroprogramm in RISC zerlegt und im Kern ausgeführt. Die einfachen Befehle werden direkt im RISC Kern in einem einzigen Datenzyklus ausgeführt. Alle wichtigen elementaren (Risc) Befehle werden direkt von Level 0 ( der Hardware ) ausgeführt und somit nicht via Mikroinstruktionen interpretiert. Dies ist ein Vorteil von reinen RISC Systemen, welche diese Interpretationsebene zwischen Hardware und ISA (Instruction Set Architecture) Ebene nicht durchlaufen müssen. Mikroinstruktionen steuern den Datenweg für einen Zyklus. Sie enthält alle notwendigen Bit-Belegungen für ALU, MEM, Register etc., um einen Zyklus abarbeiten lassen zu können. Die Adresse der nächsten Mikroinstruktion wird ebenso mit codiert, wie die Art und Weise des Aufrufes. Die Mikroinstruktionen werden in einem Steuerspeicher gehalten, welcher das jeweilige Mikroprogramm enthält. Der Steuerspeicher muss die Mikroinstruktionen nicht in geordneter oder sequentieller Folge enthalten, wie es beim Hauptspeicher der Fall ist. Es kann jede Instruktion einen Verweis auf die Nächste enthalten. Sprünge sind einfach möglich. Angewandt wird dies in Form von Opcodes, welche nichts anderes als Adressen auf Mikroinstruktionen im Steuerspeicher sind. Kapitel 6 - Pipelining Wozu dient Pipelining? Pipelining soll es ermöglichen Befehle überlappt auszuführen. Dazu sind ein einheitliches Befehlsformat fester Länge Grundlage. Deshalb wer

Summary

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |