Mit normalen Pipelines (Überlappen von Instruktionen) ist nur eine maximale Performance von einem Befehl / Takt technisch und theoretisch möglich. Um diese Grenze zu unterschreiten, ist Parallelität auf Befehlsebene (Instruction Level Parallelism) notwendig. Dies bedeutet das der typische Risc-Prozessor, um Einiges erweitert werden muss:

- Prozessor muss in der Lage sein, mehrere Befehle gleichzeitig pro Takt zu laden

- Branches dürfen möglichst nicht zur Behinderung des Befehlsflusses führen (deshalb Sprungvorhersage)

- Datenabhängigkeiten treten hier in erhöhtem Maße auf und müssen behandelbar sein

- um echte Datenabhängigkeiten auflösen zu können, is Out-Of-Order Ausführung mit anschließender "Sortierung" notwendig

Static Scheduling nutzt lediglich Compilertechniken zur Separierung unabhängiger Befehle und ist sehr unflexibel. Beim Dynamic Scheduling wird durch Präsenz mehrerer paralleler Buffer und Execution Units versucht, Ressourcen- und Datenkonflikte zu eliminieren.

Out-Of-Order Execution

In-Order-Issue Pipes müssen, falls ein Befehle gestoppt wird, alle Folgebefehle warten. Durch eine zusätzliche Hardware, welche das Umordnen der Befehlsausführung zur Laufzeit vornimmt, kann dies verhindert werden. Möglichkeiten dafür sind Scoreboards oder Tomasulo.

Was ist das Problem des Präzisen Zustandes?

Das Prinzip des Präzisen Zustandes besagt, daß bei Unterbrechungen (Interrupts, Exeptions) der Zustand der CPU sicherbar und wiederherstellbar sein muss. Dieses Konzept muss auch bei superskalaren Architekturen gelten. Dies ist in superskalaren Architekturen weitaus aufwendiger und bedarf zusätzlicher Hardware.

Welche Entwurfskriterien sind zu betrachten?

- Stategien zum holen mehrerer Instruktionen pro Takt (und Einfluss von Branches)

- Methoden zum Auffinden von Datenabhängigkeiten zwischen Registerinhalten

- Methoden zum Aussenden (Issue) mehrerer Befehle gleichzeitig

- Ressourcen zur paralellen Ausführung (mehrere Ausführungseinheiten und Zwischenbuffer)

- Ausführung mehrerer LOAD/STORE-Pipelines in enger Abstimmung mit Ausführungseinheiten (LOAD/STORE Instruktionen müssen entkoppelt auf Grund der verschiedenen Latenzzeiten ablaufen können)

- Methoden zur Bestimmung der korrekten Ausführungsreihenfolge und Speicherfolge der Register

Beide Techniken senden mehr als nur einen Befehl pro Taktzyklus aus und versuchen so, die CPI unter eins zu drücken. Moderne Prozessoren kombinieren beide Techniken. Der größte Unterschied zwischen beiden Technologien besteht darin, daß Very Long Instruction Word basierende Systeme für verschiedene Prozessoren neu compiliert werden muss. Superskalare-Prozessoren sind dagegen gleich kompatibel.

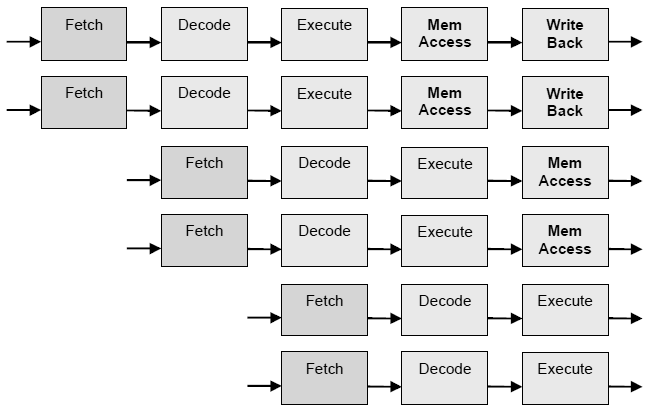

Was heißt Multiple-Issu?Ist das Mehrfach-Aussenden von Befehlen, welchen gewissen issue criteria unterliegen müssen. Die folgende Abbildung zeigt das Superskalarprinzip - eine 5-stufige Pipeline mit zweifacher Superskalarität.

Abb.: zweifach superskalare fünfstufige Pipeline

Superskalarität mit VLIW

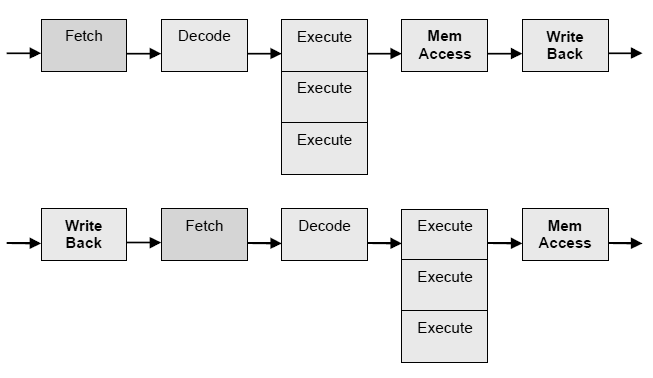

Der IA-64-Befehlssatz von Intel wird auf "Very Long Instruction Words" basieren. Es werden drei Instruktionen ein einen fetten 128 Bit Befehl gepackt. Hier besteht nun die Möglichkeit, explizit festzulegen, welche Befehle parallel abgearbeitet werden sollen bzw. können. So eröffnen sich völlig neue Optimierungsmöglichkeiten im Compilerbau. Man nennt dieses Prinzip EPIC. Der Transmeta verwendet auch VLIW. Hier muss aber der Compiler nicht die Optimierungen vornehmen, da der Transmeta um der Core eine Morphing Softwareebene hat, welche die Aufteilung in parallel abarbeitbare Befehle ausführt. Dadurch, daß nun explizit gesagt wird, welche Instruktionen parallel ausführbar sind, ist nun nicht mehr so viel Chipfläche zum Auflösen von Hazards notwendig und kann z.B. für mehr Register verwendet werden.

Abb.: Prinzip VLIW mit drei Superbefehlen

Grundprinzipien der Rechnerarchitektur

e simuliert. Hier sinkt die Fehlvorhersage von 20% auf unter 8%! Beim GCC-Compiler sind dagegen keine Unterschiede zwischen Correlating Predictors und normaler 2-Bit Sprungvorhersage erkennbar. <span>Kapitel 8 - Superskalarität Was bedeutet superskalar? Mit normalen Pipelines (Überlappen von Instruktionen) ist nur eine maximale Performance von einem Befehl / Takt technisch und theoretisch möglich. Um diese Grenze zu unterschreiten, ist Parallelität auf Befehlsebene (Instruction Level Parallelism) notwendig. Dies bedeutet das der typische Risc-Prozessor, um Einiges erweitert werden muss: Prozessor muss in der Lage sein, mehrere Befehle gleichzeitig pro Takt zu laden Branches dürfen möglichst nicht zur Behinderung des Befehlsflusses führen (deshalb Sprungvorhersage) Datenabhängigkeiten treten hier in erhöhtem Maße auf und müssen behandelbar sein um echte Datenabhängigkeiten auflösen zu können, is Out-Of-Order Ausführung mit anschließender "Sortierung" notwendig Dynamic Scheduling Static Scheduling nutzt lediglich Compilertechniken zur Separierung unabhängiger Befehle und ist sehr unflexibel. Beim Dynamic Scheduling wird durch Präsenz mehrerer paralleler Buffer und Execution Units versucht, Ressourcen- und Datenkonflikte zu eliminieren. Out-Of-Order Execution In-Order-Issue Pipes müssen, falls ein Befehle gestoppt wird, alle Folgebefehle warten. Durch eine zusätzliche Hardware, welche das Umordnen der Befehlsausführung zur Laufzeit vornimmt, kann dies verhindert werden. Möglichkeiten dafür sind Scoreboards oder Tomasulo. Was ist das Problem des Präzisen Zustandes? Das Prinzip des Präzisen Zustandes besagt, daß bei Unterbrechungen (Interrupts, Exeptions) der Zustand der CPU sicherbar und wiederherstellbar sein muss. Dieses Konzept muss auch bei superskalaren Architekturen gelten. Dies ist in superskalaren Architekturen weitaus aufwendiger und bedarf zusätzlicher Hardware. Welche Entwurfskriterien sind zu betrachten? Stategien zum holen mehrerer Instruktionen pro Takt (und Einfluss von Branches) Methoden zum Auffinden von Datenabhängigkeiten zwischen Registerinhalten Methoden zum Aussenden (Issue) mehrerer Befehle gleichzeitig Ressourcen zur paralellen Ausführung (mehrere Ausführungseinheiten und Zwischenbuffer) Ausführung mehrerer LOAD/STORE-Pipelines in enger Abstimmung mit Ausführungseinheiten (LOAD/STORE Instruktionen müssen entkoppelt auf Grund der verschiedenen Latenzzeiten ablaufen können) Methoden zur Bestimmung der korrekten Ausführungsreihenfolge und Speicherfolge der Register Superskalare Prozessoren müssen nicht die Instruktionssequentialität (siehe out-of-order-execution)einhalten, jedoch immer die Ergebnissequentialität (siehe in-order-commit). Superskalar-Prozessoren und VLIW-Prozessoren als Multipe-Issue CPU's Beide Techniken senden mehr als nur einen Befehl pro Taktzyklus aus und versuchen so, die CPI unter eins zu drücken. Moderne Prozessoren kombinieren beide Techniken. Der größte Unterschied zwischen beiden Technologien besteht darin, daß Very Long Instruction Word basierende Systeme für verschiedene Prozessoren neu compiliert werden muss. Superskalare-Prozessoren sind dagegen gleich kompatibel. Was heißt Multiple-Issu? Ist das Mehrfach-Aussenden von Befehlen, welchen gewissen issue criteria unterliegen müssen. Die folgende Abbildung zeigt das Superskalarprinzip - eine 5-stufige Pipeline mit zweifacher Superskalarität. Abb.: zweifach superskalare fünfstufige Pipeline Superskalarität mit VLIW Der IA-64-Befehlssatz von Intel wird auf "Very Long Instruction Words" basieren. Es werden drei Instruktionen ein einen fetten 128 Bit Befehl gepackt. Hier besteht nun die Möglichkeit, explizit festzulegen, welche Befehle parallel abgearbeitet werden sollen bzw. können. So eröffnen sich völlig neue Optimierungsmöglichkeiten im Compilerbau. Man nennt dieses Prinzip EPIC. Der Transmeta verwendet auch VLIW. Hier muss aber der Compiler nicht die Optimierungen vornehmen, da der Transmeta um der Core eine Morphing Softwareebene hat, welche die Aufteilung in parallel abarbeitbare Befehle ausführt. Dadurch, daß nun explizit gesagt wird, welche Instruktionen parallel ausführbar sind, ist nun nicht mehr so viel Chipfläche zum Auflösen von Hazards notwendig und kann z.B. für mehr Register verwendet werden. Abb.: Prinzip VLIW mit drei Superbefehlen Das Scoreboard Ein Scoreboard ist eine zusätzliche Steuereinheit, welche die Verantwortung für das Befehlsaussenden und das Erkennen von Konflikten trägt. Das Scoreboard wählt aus einem

Summary

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |