Edited, memorised or added to reading queue

on 17-Jul-2024 (Wed)

Do you want BuboFlash to help you learning these things? Click here to log in or create user.

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) <span>Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC

Original toplevel document

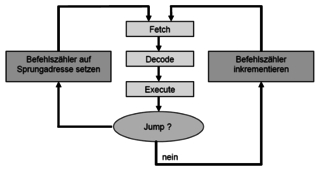

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open iteichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. <span>Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open it(CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? <span>Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Au

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itWas heißt Havard-Architektur? [Havard-Architektur] Daten- und Befehlsspeicher sind getrennt. [Havard-Architektur] So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. [Havard-Architektur] Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei E

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itWas heißt Havard-Architektur? [Havard-Architektur] Daten- und Befehlsspeicher sind getrennt. [Havard-Architektur] So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. [Havard-Architektur] Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert.

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itspan> Was heißt Havard-Architektur? [Havard-Architektur] Daten- und Befehlsspeicher sind getrennt. [Havard-Architektur] So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. <span>[Havard-Architektur] Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. <span>

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itvier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. <span>Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. <span>

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open iterechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. <span>Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. <span>

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itWie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Wie kann die Leistung erhöht werden? Über Optimierung von Software Compileroptimierung Wie kann die Leistung erhöht werden? Über die Siliziumbasis Transistordichte und Taktraten

Original toplevel document

Grundprinzipien der Rechnerarchitekturon Kapitel 8 - Superskalarität Kapitel 9 - Parallelrechner Zurück zur Übersicht Rechnerarchitektur Grundprinzipien der Rechnerarchitektur. D.h. Themen wie RISC, Branch Prediction oder Tomasulo. <span>Kapitel 1 - Prinzipien und Architekturen In welche sieben Ebenen kann man ein Rechnersystem einteilen? Anwendungsebene (Anwendersoftware) Assemblerebene (Beschreibung von Algorithmen, Link & Bind) Betriebssystem (Speichermanagment, Prozesskommunikation) Instruction Set Architecture (ISA,Adressierungsarten) Microarchitektur (Risc,Cisc,Branch Prediction..) Logische Ebene (Register,Schieber, Latches..) Transistorebene (Transistoren, MOS ) nach Tanenbaum Computerarchitektur Wie lassen sich Architekturen klassifizieren? Nach ihrem Rechenprinzip Von Neumann (Steuerfluss) Datenfluß (Zündregel) Reduktion (Funktionsaufruf) Objektorientiert (Methodenaufruf) Nach dem Architektur-Grundkonzept Vektorrechner (Pipeline) Array-Computer (Data-Array) Assoziativ-Rechner (Assoziativ-Speicher) Wie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Über Optimierung von Software Compileroptimierung Über die Siliziumbasis Transistordichte und Taktraten Was sind die vier Hauptbestandteile eines typischen Rechners? Was unterscheidet eine Schnittstelle von einem Bus? Ein Bus verbindet mehr als zwei Teilnehmer. John von Neumann mit ENIAC Welche Bestandteile definieren einen von Neumann-Rechner? Der von Neumann-Rechner arbeitet sequentiell, Befehl für Befehl wird abgeholt, interpretiert, ausgeführt und das Resultat abgespeichert. Steuerwerk (Taktgeber und Befehlszähler) Speicher Rechenwerk (CPU) I/O-Einheit Datenbreite, Adressierungsbreite, Registeranzahl und Befehlssatz können als Parameter verstanden werden. Wie arbeitet die zentrale Befehlsschleife eines Von-Neumann-Rechners? Was heißt Havard-Architektur? Daten- und Befehlsspeicher sind getrennt. So ist es möglich Daten und Befehle Zeitgleich aus dem Speicher zu holen. Da dies aber einen extrem hohen Aufwand bedeutet, wird dies nur bei Echtzeitanwendungen implementiert. Was ist ein Taktzyklus? Die Interpretation und Ausführung eines Befehles erfolgt in vier Phasen. Holen Dekodieren (inklusive Operandenadressen berechnen) Daten holen (bzw. Operanden) Ausführen Jede der vier Phasen wird in eine Anzahl von Schnittstellen bzw. Zyklen eingeteilt. Ein Taktzyklus ist die kleinstmöglich verarbeitbare Einheit. Somit benötigt ein Befehl zur Ausführung im Allgemeinen mehr als einen Taktzyklus. Was ist Mikroprogrammierung? Durch Einsatz von Matrix-Speichertechnologie ist es möglich Steuersignalkombinationen in je einer Zeile dieser Speichermatrix abzulegen. Somit können Zeile für Zeile Maschinenzustande auf dem Prozessor hinterlegt werden. Das sogenannte Mikroprogramm. Die interne Logik ist eher zufällig optimiert. Daher der Begriff "Random Logic". Was sind Complex Instruction Set Computer (CISC)? Durch Einführung von mnemonischen Kodierungen von Mikrobefehlen, welche von Mikrobefehls-Assemblern verarbeitet werden, sind weitaus komplexere Befehle möglich. CISC bietet einen sehr großen Befehlssatz mit sich start unterscheidenden Befehlen in Ausführungszeit und Parameterliste. Gegenüberstellung der Architektur von CISC und RISC Worin unterscheiden sich RISC und CISC besonders? Eigenschaften CISC RISC Register Wenige Register( ca. 20) Viele Register (bis zu 200) und Registerfenster Befehlssatz ca. 300 Befehle und mehr als 50 Befehlstypen Nur rund 100 meist registerorientierte Befehle (außer LOAD / STORE) Adressierungsarten ca. 12 verschiedene Nur 3 bis 5 Arten und nur LOAD/STORE zum Speicher Caches Gemeinsame Caches, aber später auch Getrennte Getrennte Daten- und Befehlscaches nach Harvard CPI 1 bis 20 - Durchschnittlich 4 1 bei Basisoperationen - im Schnitt 1,5 Befehlssteuerung Mikrocode im Speicher, aber auch hartverdrahtet Meistens hartverdrahtete Mikroprogramme ohne Mikroprogrammspeicher Beispielprozessoren Intel x86, AMD, Cyrix Sun UltraSparc, PowerPC Welche Befehlssatz-Architekturen kennen Sie? Stack-Architektur? Diese Form benötigt keine Adressen für Operanden und ist somit eine Nulladressmaschine. Quell und Ergebnisoperanden liegen auf einem Operanden-Stack. Vorteil dieser Architektur ist daher die Speicherplatzeinsparung durch die nicht notwendigen Adressen. Akkumulator-Architektur? Um Verknüpfungsoperationen durchzuführen, liegt ein Operand in einem Register und ein Operand typischerweise im Hauptspeicher (Einadressmaschine) . Vorteil ist die einfache Implementierung, da nur ein internes Register benötigt wird. Nachteil ist aber die hohe Speicherlast. Universalregister-Architektur? Ein Satz von gleichberechtigten Registern kann zum Ablegen von Daten genutzt werden. Deshalb sind im Op-Code mehrere Operanden anzugeben (Zwei-, Dreiadressmaschine etc.) Vorteil ist die freie Benutzbarkeit durch Compiler. Ausdrucksberechnungen können somit in beliebiger Reihenfolge erfolgen, was Pipelining möglich macht. Dazu kommt, daß die Speichertransferlast sinkt, die Geschwindigkeit steigt und Superskalartechniken sind effizient einsetzbar. Der Nachteil dieser Architektur sind die teilweise großen Registersets, welche bei jedem Kontextwechsel auszutauschen sind. Außerdem müssen die Operanden Adressiert werden, was zu langen Befehlen führt. Welche Register-Architekturen gibt es? Register-Register ohne Speicheradressen (Sparc,Mips) Verknüpfungsoperationen verwenden nur Register. Nur in Lade- und Speicherbefehlen werden Adressen verwendet. (Load / Store - Architektur). Vorteil ist, dass die Verknüpfungen immer mit Registern geschehen und somit eine Befehlsdekodierung mit fester Länge möglich ist. Vorteile Einheitliche Taktzyklen pro Befehl Pipeline-Prinzip wird dadurch unterstützt Nachteile Code wird größer, da Speichertransfers nur durch zusätzliche Befehle Register-Speicher mit der Möglichkeit von Speicheradressen (Motorola 68000) Vorteile Daten können auch im Speicher referenziert werden, ohne diese vorher Explizit laden zu müssen. Nachteile Durch die variierenden Adressierungen variieren Befehlslänge und Taktzyklen pro Befehl, was äußerst negativ für Verfahren wie Pipelining ist. Speicher-Speicher mit nur Speicheradressen (DEC-VAX) Vorteile Der Programmierer braucht sich nicht um Register kümmern. Deshalb wird die Programmierung transparenter. Nachteile Es entsteht ein hoher Speicherverkehr, was sich Nachteilig auf die Performance auswirkt. Falls doch Register erlaubt werden (Orthogonaler Befehlssatz / CISC), variieren auch hier Befehlslänge und Taktanzahl pro Befehl. Orthogonale Befehlssätze sind solche, welche eine beliebige Kombination von Befehlscode, Adressierungsart und Datentyp zulassen. Was ist Byte-Ordering und Word-Alignment? Alle konventionellen Rechner sind Byte-Adressiert. D.h. das Worte (egal ob 8, 16 oder mehr Bit) bestehen aus einer Folge (aufsteigender) Bytes. Dabei gilt das erste Byte als die Adresse des Wortes. Nimmt die Wertigkeit mit aufsteigender Adresse zu, ist es das Litte-Endian-Format, umgekehrt das Big-Endian-Format. Falls Worte so in den Speicher passen, das keine Verschiebungen auftreten, heißt der Speicher aligned. Prüfen kann man dies durch die Formel Adresse mod Wortlänge = 0? Kapitel 2 - Interrupts und DMA Klassifizieren Sie die verschiedenen Unterbrechungen! Wenn in der Literatur von Interrupts gesprochen wird, so werden oft externe, asynchrone Interrupts g

| status | not read | reprioritisations | ||

|---|---|---|---|---|

| last reprioritisation on | suggested re-reading day | |||

| started reading on | finished reading on |

Parent (intermediate) annotation

Open itWie kann die Leistung erhöht werden? Über die Architektur Pipelines, Superskalarität, Spekulative Ausführung, Caches, Busbreite Wie kann die Leistung erhöht werden? Über Optimierung von Software Compileroptimierung Wie kann die Leistung erhöht werden? Über die Siliziumbasis Transistordichte und Taktraten

Original toplevel document